Product Summary

The CD54HC30F3A is a High Speed CMOS Logic 8-Input NAND Gate. It contains an 8-input NAND gate in one package. The CD54HC30F3A provides the system designer with the direct implementation of the positive logic 8-input NAND function. Logic gates utilize silicon gate CMOS technology to achieve operating speeds similar to LSTTL gates with the low power consumption of standard CMOS integrated circuits. The CD54HC30F3A has the ability to drive 10 LSTTL loads. The HCT logic family is functionally pin compatible with the standard LS logic family.

Parametrics

CD54HC30F3A absolute maximum ratings: (1)DC Supply Voltage, VCC:-0.5V to 7V; (2)DC Input Diode Current, IIK: For VI < -0.5V or VI > VCC + 0.5V:±20mA; (3)DC Output Diode Current, IOK: For VO < -0.5V or VO > VCC + 0.5V:±20mA; (4)DC Output Source or Sink Current per Output Pin, IO: For VO > -0.5V or VO < VCC + 0.5V:±25mA; (5)DC VCC or Ground Current, ICC or IGND:±50mA.

Features

CD54HC30F3A features: (1)Buffered Inputs; (2)Typical Propagation Delay: 10ns at VCC = 5V,CL = 15pF, TA = 25℃; (3)Fanout (Over Temperature Range):Standard Outputs:10 LSTTL Loads, Bus Driver Outputs:15 LSTTL Loads; (4)Wide Operating Temperature Range:-55℃ to 125℃; (5)Balanced Propagation Delay and Transition Times; (6)Significant Power Reduction Compared to LSTTL Logic ICs; (7)2V to 6V Operation; (8)High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V.

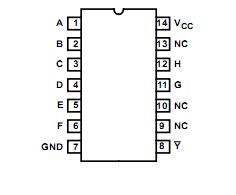

Diagrams

|

CD54 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CD54/74HC161 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CD54/74HC163 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CD54/74HC192 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CD54/74HC193 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CD54/74HC240 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))