Product Summary

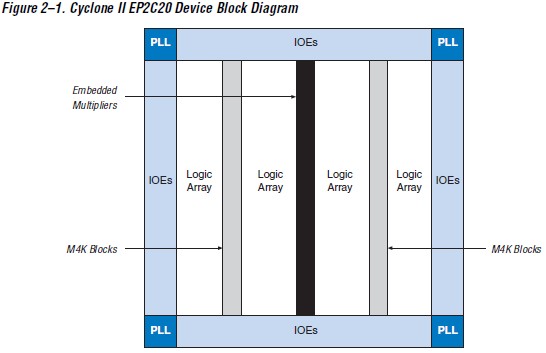

The EP2C20Q240C8 Altera Cyclone II FPGA extends the low-cost FPGA density range to 68,416 logic elements (LEs) and provide up to 622 usable I/O pins and up to 1.1 Mbits of embedded memory. It is manufactured on 300-mm wafers using TSMCs 90-nm low-k dielectric process to ensure rapid availability and low cost. By minimizing silicon area, the EP2C20Q240C8 can support complex digital systems on a single chip at a cost that rivals that of ASICs. The low cost and optimized feature set of the Cyclone II FPGA make them ideal solutions for a wide array of automotive, consumer, communications, video processing, test and measurement, and other end-market solutions. The EP2C20Q240C8 contains a two-dimensional row- and column-based architecture to implement custom logic. It ranges in density from 4,608 to 68,416 LEs.

Parametrics

EP2C20Q240C8 absolute maximum ratings: (1)VCCINT, Supply voltage With respect to ground: –0.5 to 1.8 V; (2)VCCIO, Output supply voltage: –0.5 to 4.6 V; (3)VCCA_PLL [1..4], PLL supply voltage: –0.5 to 1.8 V; (4)VIN, DC input voltage: -0.5 to 4.6 V; (5)IOUT, DC output current, per pin: -25 to 40 mA; (6)TSTG, Storage temperature, No bias: –65 to 150 ℃; (7)TJ, Junction temperature, BGA packages under bias: 125 ℃.

Features

EP2C20Q240C8 features: (1)High-density architecture with 4,608 to 68,416 LEs; (2)Embedded multipliers: Up to 150 18×18-bit multipliers are each configurable as two independent 9× 9-bit multipliers with up to 250-MHz performance; Optional input and output registers; (3)Advanced I/O support; (4)Flexible clock management circuitry: Hierarchical clock network for up to 402.5-MHz performance; Up to four PLLs per device provide clock multiplication and division, phase shifting, programmable duty cycle, and external; (5)clock outputs, allowing system-level clock management and skew control; Up to 16 global clock lines in the global clock network that drive throughout the entire device; (6)Device configuration: Fast serial configuration allows configuration times less than 100 ms; Decompression feature allows for smaller programming file storage and faster configuration times; Supports multiple configuration modes: active serial, passive serial, and JTAG-based configuration; Supports configuration through low-cost serial configuration devices; Device configuration supports multiple voltages (either 3.3, 2.5, or 1.8 V).

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP2C20Q240C8 |

|

IC CYCLONE II FPGA 20K 240-PQFP |

Data Sheet |

|

|

||||||

|

EP2C20Q240C8N |

|

IC CYCLONE II FPGA 20K 240-PQFP |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))