Product Summary

The HY6264ALLJ-10 is a high speed, low power 8,192 words by 8-bit CMOS static RAM fabricated using a twin tub CMOS process technology. This high reliability process coupled with innovative circuit design techniques, yields maximum access time of 70ns. The HY6264ALLJ-10 has a data retention mode that guarantees data to remain valid at a minimum power supply voltage of 2.0volt. Using CMOS technology, supply voltage from 2.0 to 5.5volt have little effect on supply current in data retention mode. Reducing the supply voltage to minimize current drain is unnecessary with the HY6264ALLJ-10 family.

Parametrics

HY6264ALLJ-10 absolute maximum ratings: (1)power supply, input, input/output voltage:-0.5V to 7.0V; (2)temperature under bias:-10℃ to 125℃; (3)storage temperature:-65℃ to 150℃; (4)power dissipation:1.0W; (5)data output current:50mA.

Features

HY6264ALLJ-10 features: (1)high speed-70/85/100/120/150ns(max.); (2)low power consumption: 200mW typical operating, 10μW typical standby; (3)battery back up:2 volt data retention; (4)fully static operation: no clock or refresh required; (5)all inputs and outputs directly TTL compatible; (6)tri-state output; (7)high reliability 28 pin 600 mil P-DIP and 300 mil SOP.

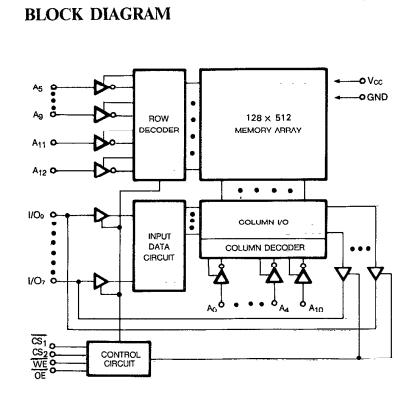

Diagrams

|

HY62256A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY62256A-I |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY628100A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY628100B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY628100BLLG-55 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HY628100BLLT1-70 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))